#

## Keysight Technologies 86108B Precision Waveform Analyzer

### Data Sheet

Engineered for easy and accurate characterization of high-speed electrical designs from 50 Mb/s to 32 Gb/s.

#### Unprecedented performance

- Bandwidths to 50 GHz

- Ultra-low timebase jitter < 50 fs rms (typical)

- Integrated clock recovery (CR) to 32 Gb/s

- Adjustable clock recovery loop bandwidth/peaking

#### Unmatched value and flexibility

- Lowest cost oscilloscope solution for 1 0-28 Gb/s signals

- Continuous data rate coverage from 50 Mb/s to 32 Gb/s

- Simple and easy connections

- Upgradable hardware (BW and CR options)

#### Advanced analysis capability

- Jitter Spectrum Analysis

- PLL characterization including loop BW/jitter transfer

- Analyze closed eyes using trigger from Aux CR input

As high-speed electrical communication systems and components increase in data rates to 25 Gb/s and beyond, design and validation engineers are faced with the difficult task of accurately characterizing the true performance of their designs. The Keysight Technologies, Inc. 86108B Precision Waveform Analyzer is a plug-in module used with the 86100C/D Infiniium DCA family of oscilloscopes that provides an ideal solution to this measurement challenge. With industry-best residual jitter well below 70 femtoseconds (<50 fs typical!), channel bandwidths to 50 GHz, and an integrated instrumentation-grade hardware clock recovery circuit, the 86108B is engineered to provide accurate jitter analysis, eye diagram, and waveform characterization on signals from 50 Mb/s to 32 Gb/s. The 86108B provides a "gold standard" for waveform accuracy and translates into confidence that the waveform displayed by the oscilloscope is a faithful representation of the true device performance.

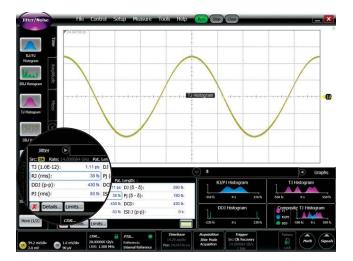

Jitter measurement showing an RJ component of 38 fs, indicating the ultra-low residual jitter of the 86108B's integrated clock recovery and timebase.

## Configured for accuracy, compliance, and ease-of-use

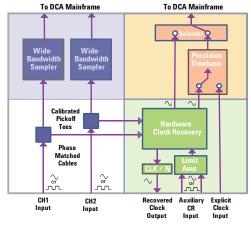

Measurement precision is achieved by integrating channels, clock recovery, and a precision timebase into a single plug-in module (see 86108B block diagram). While this is a key enabler for the high performance of the instrument, it also provides significant ease-of-use advantages; simply connect either a single-ended or differential signal to the channel inputs and start making measurements. There is no need for extra cables or splitters since the module includes a calibrated pickoff circuit and phase matched cables. An instrument grade hardware clock recovery (CR) system operates at any rate from 50 Mb/s to 32 Gb/s (Option 232) and offers adjustable loop bandwidth and peaking capability to ensure compliant measurements. Integration of the system hardware virtually eliminates the trigger-to-sample delay inherent in sampling oscilloscopes.

#### Reference Clock and Phase-Locked Loop (PLL) Characterization

An on-board phase detector, part of the 86108B's internal clock recovery circuit, enables accurate jitter spectrum/phase noise measurements of the incoming signal using Keysight 86100DU-400 software. When the 86108B is used with a jitter source<sup>1</sup>, this application also makes it easy to perform compliant PLL bandwidth and peaking measurements for most PLL designs, including PCI Express (Gen 1/2/3).

See www.keysight.com/find/jtf for further details.

- 2 Compatible with 86100C/D DCA mainframes (FW Rev A.10.70 or later).

- 3 Upgradable hardware option (Return to a Keysight Service Center).

4 Included as a standard (no cost) option.

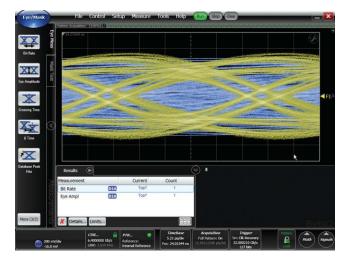

The Auxiliary clock recovery input makes it possible to analyze, and equalize, closed eyes.

#### Working with closed eyes?

After a high-speed signal has passed through a backplane or some other lossy path, the inter-symbol interference (ISI) that is introduced may close the eye diagram entirely. Hardware clock recovery circuits rely on their ability to detect transitions in the incoming pattern, but if the signal is severely impaired due to ISI, these edges may not be detectable. For a situation like this, or for very low level signals (in the tens of mV), the 86108B features an auxiliary CR input circuit. Analyze the degraded signal and/or apply a software CTLE, for example, by triggering the scope using a separate (and clean) synchronous data or clock signal connected to the 86108B's Aux CR Input. A limit amp on this input also mitigates the impact of AM to PM conversion (due to noise on slow edges) on the recovered clock.

#### 86108B Precision Waveform Analyzer<sup>2</sup> Bandwidth Options<sup>3</sup> (choose either LBW or HBW):

| _ | 86108B-LBW |   |     | 35 | GHz E | Bandwid <sup>.</sup> | th |

|---|------------|---|-----|----|-------|----------------------|----|

| _ | 86108B-HBW |   |     | 50 | GHz E | Bandwid <sup>.</sup> | th |

|   |            | ~ | 1.1 |    | 0 ( ) |                      |    |

#### Clock Recovery Options<sup>3</sup> (choose either 216 or 232):

- 86108B-216

- 86108B-232 50 Mb/s to 32 Gb/s (continuous)

- 86108B-300<sup>4</sup> Adjustable Loop Bandwidth

- (15 kHz to 20 MHz) and Peaking Auxiliary Clock Recovery Input

50 Mb/s to 16 Gb/s (continuous)

#### - 86108B-400<sup>4</sup> Precision Timebase:

- 86108B-PTB<sup>4</sup>

- Integrated Precision Timebase < 50 fs rms residual jitter (typical)

#### www.keysight.com/find/86108B

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

This information is subject to change without notice. © Keysight Technologies, 2012 - 2014 Published in USA, August 2, 2014 5990-9754EN www.keysight.com

Jitter sources for the PLL BW/jitter transfer measurement include the Keysight N4903 JBERT, 81150, 81160, N5182A MXA, or pattern generators/sources with delay line or phase modulation inputs modulated with a 33250A function generator."